MIOS32_SPI

Defines | |

| #define | MIOS32_SPI0_PTR LPC_SSP0 |

| #define | MIOS32_SPI0_RCLK1_INIT { MIOS32_SYS_LPC_PINSEL(1, 21, 0); MIOS32_SYS_LPC_PINDIR(1, 21, 1); } |

| #define | MIOS32_SPI0_RCLK1_SET(v) { MIOS32_SYS_LPC_PINSET(1, 21, v); } |

| #define | MIOS32_SPI0_RCLK2_INIT { MIOS32_SYS_LPC_PINSEL(1, 22, 0); MIOS32_SYS_LPC_PINDIR(1, 22, 1); } |

| #define | MIOS32_SPI0_RCLK2_SET(v) { MIOS32_SYS_LPC_PINSET(1, 22, v); } |

| #define | MIOS32_SPI0_SCLK_INIT { MIOS32_SYS_LPC_PINSEL(1, 20, 3); } |

| #define | MIOS32_SPI0_MISO_INIT { MIOS32_SYS_LPC_PINSEL(1, 23, 3); } |

| #define | MIOS32_SPI0_MOSI_INIT { MIOS32_SYS_LPC_PINSEL(1, 24, 3); } |

| #define | MIOS32_SPI0_PP_INIT { LPC_PINCON->PINMODE_OD1 &= ~((1 << 24) | (1 << 23) | (1 << 22) | (1 << 21) | (1 << 20)); } |

| #define | MIOS32_SPI0_OD_INIT { LPC_PINCON->PINMODE_OD1 |= ((1 << 24) | (1 << 23) | (1 << 22) | (1 << 21) | (1 << 20)); } |

| #define | MIOS32_SPI0_IN_INIT |

| #define | MIOS32_SPI0_DMA_TX_REQ 0 |

| #define | MIOS32_SPI0_DMA_RX_REQ 1 |

| #define | MIOS32_SPI0_DMA_TX_CHN 0 |

| #define | MIOS32_SPI0_DMA_RX_CHN 1 |

| #define | MIOS32_SPI1_PTR LPC_SSP1 |

| #define | MIOS32_SPI1_RCLK1_INIT { MIOS32_SYS_LPC_PINSEL(0, 6, 0); MIOS32_SYS_LPC_PINDIR(0, 6, 1); } |

| #define | MIOS32_SPI1_RCLK1_SET(v) { MIOS32_SYS_LPC_PINSET(0, 6, v); } |

| #define | MIOS32_SPI1_RCLK2_INIT { MIOS32_SYS_LPC_PINSEL(3, 26, 0); MIOS32_SYS_LPC_PINDIR(3, 26, 1); } |

| #define | MIOS32_SPI1_RCLK2_SET(v) { MIOS32_SYS_LPC_PINSET(3, 26, v); } |

| #define | MIOS32_SPI1_SCLK_INIT { MIOS32_SYS_LPC_PINSEL(0, 7, 2); } |

| #define | MIOS32_SPI1_MISO_INIT { MIOS32_SYS_LPC_PINSEL(0, 8, 2); } |

| #define | MIOS32_SPI1_MOSI_INIT { MIOS32_SYS_LPC_PINSEL(0, 9, 2); } |

| #define | MIOS32_SPI1_PP_INIT { LPC_PINCON->PINMODE_OD0 &= ~((1 << 9) | (1 << 8) | (1 << 7) | (1 << 6)); LPC_PINCON->PINMODE_OD3 &= ~((1 << 26)); } |

| #define | MIOS32_SPI1_OD_INIT { LPC_PINCON->PINMODE_OD0 |= ((1 << 9) | (1 << 8) | (1 << 7) | (1 << 6)); LPC_PINCON->PINMODE_OD3 |= ((1 << 26)); } |

| #define | MIOS32_SPI1_IN_INIT |

| #define | MIOS32_SPI1_DMA_TX_REQ 2 |

| #define | MIOS32_SPI1_DMA_RX_REQ 3 |

| #define | MIOS32_SPI1_DMA_TX_CHN 2 |

| #define | MIOS32_SPI1_DMA_RX_CHN 3 |

| #define | MIOS32_SPI2_PTR LPC_SPI |

| #define | MIOS32_SPI2_RCLK1_INIT { MIOS32_SYS_LPC_PINSEL(0, 16, 0); MIOS32_SYS_LPC_PINDIR(0, 16, 1); } |

| #define | MIOS32_SPI2_RCLK1_SET(v) { MIOS32_SYS_LPC_PINSET(0, 16, v); } |

| #define | MIOS32_SPI2_RCLK2_INIT { MIOS32_SYS_LPC_PINSEL(0, 21, 0); MIOS32_SYS_LPC_PINDIR(0, 21, 1); } |

| #define | MIOS32_SPI2_RCLK2_SET(v) { MIOS32_SYS_LPC_PINSET(0, 21, v); } |

| #define | MIOS32_SPI2_SCLK_INIT { MIOS32_SYS_LPC_PINSEL(0, 15, 3); } |

| #define | MIOS32_SPI2_MISO_INIT { MIOS32_SYS_LPC_PINSEL(0, 17, 3); } |

| #define | MIOS32_SPI2_MOSI_INIT { MIOS32_SYS_LPC_PINSEL(0, 18, 3); } |

| #define | MIOS32_SPI2_PP_INIT { LPC_PINCON->PINMODE_OD0 &= ~((1 << 21) | (1 << 18) | (1 << 17) | (1 << 16) | (1 << 15)); } |

| #define | MIOS32_SPI2_OD_INIT { LPC_PINCON->PINMODE_OD0 |= ((1 << 21) | (1 << 18) | (1 << 17) | (1 << 16) | (1 << 15)); } |

| #define | MIOS32_SPI2_IN_INIT |

| #define | MIOS32_SPI0_DMA_IRQHANDLER_FUNC void DMAChannel2_IRQHandler(void) |

| #define | MIOS32_SPI1_DMA_IRQHANDLER_FUNC void DMAChannel4_IRQHandler(void) |

| #define | MIOS32_SPI2_DMA_IRQHANDLER_FUNC NULL |

| #define | MIOS32_SPI0_PTR SPI1 |

| #define | MIOS32_SPI0_DMA_RX_PTR DMA1_Channel2 |

| #define | MIOS32_SPI0_DMA_TX_PTR DMA1_Channel3 |

| #define | MIOS32_SPI0_DMA_RX_IRQ_FLAGS (DMA1_FLAG_TC2 | DMA1_FLAG_TE2 | DMA1_FLAG_HT2 | DMA1_FLAG_GL2) |

| #define | MIOS32_SPI0_DMA_IRQ_CHANNEL DMA1_Channel2_IRQn |

| #define | MIOS32_SPI0_DMA_IRQHANDLER_FUNC void DMA1_Channel2_IRQHandler(void) |

| #define | MIOS32_SPI0_RCLK1_PORT GPIOA |

| #define | MIOS32_SPI0_RCLK1_PIN GPIO_Pin_4 |

| #define | MIOS32_SPI0_RCLK2_PORT GPIOC |

| #define | MIOS32_SPI0_RCLK2_PIN GPIO_Pin_15 |

| #define | MIOS32_SPI0_SCLK_PORT GPIOA |

| #define | MIOS32_SPI0_SCLK_PIN GPIO_Pin_5 |

| #define | MIOS32_SPI0_MISO_PORT GPIOA |

| #define | MIOS32_SPI0_MISO_PIN GPIO_Pin_6 |

| #define | MIOS32_SPI0_MOSI_PORT GPIOA |

| #define | MIOS32_SPI0_MOSI_PIN GPIO_Pin_7 |

| #define | MIOS32_SPI1_PTR SPI2 |

| #define | MIOS32_SPI1_DMA_RX_PTR DMA1_Channel4 |

| #define | MIOS32_SPI1_DMA_TX_PTR DMA1_Channel5 |

| #define | MIOS32_SPI1_DMA_RX_IRQ_FLAGS (DMA1_FLAG_TC4 | DMA1_FLAG_TE4 | DMA1_FLAG_HT4 | DMA1_FLAG_GL4) |

| #define | MIOS32_SPI1_DMA_IRQ_CHANNEL DMA1_Channel4_IRQn |

| #define | MIOS32_SPI1_DMA_IRQHANDLER_FUNC void DMA1_Channel4_IRQHandler(void) |

| #define | MIOS32_SPI1_RCLK1_PORT GPIOB |

| #define | MIOS32_SPI1_RCLK1_PIN GPIO_Pin_12 |

| #define | MIOS32_SPI1_SCLK_PORT GPIOB |

| #define | MIOS32_SPI1_SCLK_PIN GPIO_Pin_13 |

| #define | MIOS32_SPI1_MISO_PORT GPIOB |

| #define | MIOS32_SPI1_MISO_PIN GPIO_Pin_14 |

| #define | MIOS32_SPI1_MOSI_PORT GPIOB |

| #define | MIOS32_SPI1_MOSI_PIN GPIO_Pin_15 |

| #define | MIOS32_SPI2_PTR NULL |

| #define | MIOS32_SPI2_DMA_RX_PTR NULL |

| #define | MIOS32_SPI2_DMA_TX_PTR NULL |

| #define | MIOS32_SPI2_DMA_RX_IRQ_FLAGS 0 |

| #define | MIOS32_SPI2_DMA_IRQ_CHANNEL NULL |

| #define | MIOS32_SPI2_DMA_IRQHANDLER_FUNC NULL |

| #define | MIOS32_SPI2_RCLK1_PORT GPIOC |

| #define | MIOS32_SPI2_RCLK1_PIN GPIO_Pin_13 |

| #define | MIOS32_SPI2_RCLK2_PORT GPIOC |

| #define | MIOS32_SPI2_RCLK2_PIN GPIO_Pin_14 |

| #define | MIOS32_SPI2_SCLK_PORT GPIOB |

| #define | MIOS32_SPI2_SCLK_PIN GPIO_Pin_6 |

| #define | MIOS32_SPI2_MISO_PORT GPIOB |

| #define | MIOS32_SPI2_MISO_PIN GPIO_Pin_7 |

| #define | MIOS32_SPI2_MOSI_PORT GPIOB |

| #define | MIOS32_SPI2_MOSI_PIN GPIO_Pin_5 |

| #define | MIOS32_SPI2_SET_MOSI(b) { MIOS32_SPI2_MOSI_PORT->BSRR = (b) ? MIOS32_SPI2_MOSI_PIN : (MIOS32_SPI2_MOSI_PIN << 16); } |

| #define | MIOS32_SPI2_GET_MISO ( MIOS32_SPI2_MISO_PORT->IDR & MIOS32_SPI2_MISO_PIN ) |

| #define | MIOS32_SPI2_SET_SCLK_0 { MIOS32_SPI2_SCLK_PORT->BRR = MIOS32_SPI2_SCLK_PIN; } |

| #define | MIOS32_SPI2_SET_SCLK_1 { MIOS32_SPI2_SCLK_PORT->BSRR = MIOS32_SPI2_SCLK_PIN; } |

| #define | CCR_ENABLE ((uint32_t)0x00000001) |

| #define | MIOS32_SPI0_PTR SPI1 |

| #define | MIOS32_SPI0_DMA_RX_PTR DMA2_Stream2 |

| #define | MIOS32_SPI0_DMA_RX_CHN DMA_Channel_3 |

| #define | MIOS32_SPI0_DMA_RX_IRQ_FLAGS (DMA_FLAG_TCIF2 | DMA_FLAG_TEIF2 | DMA_FLAG_HTIF2 | DMA_FLAG_FEIF2) |

| #define | MIOS32_SPI0_DMA_TX_PTR DMA2_Stream3 |

| #define | MIOS32_SPI0_DMA_TX_CHN DMA_Channel_3 |

| #define | MIOS32_SPI0_DMA_TX_IRQ_FLAGS (DMA_FLAG_TCIF3 | DMA_FLAG_TEIF3 | DMA_FLAG_HTIF3 | DMA_FLAG_FEIF3) |

| #define | MIOS32_SPI0_DMA_IRQ_CHANNEL DMA2_Stream2_IRQn |

| #define | MIOS32_SPI0_DMA_IRQHANDLER_FUNC void DMA2_Stream2_IRQHandler(void) |

| #define | MIOS32_SPI0_RCLK1_PORT GPIOB |

| #define | MIOS32_SPI0_RCLK1_PIN GPIO_Pin_2 |

| #define | MIOS32_SPI0_RCLK1_AF { } |

| #define | MIOS32_SPI0_RCLK2_PORT GPIOD |

| #define | MIOS32_SPI0_RCLK2_PIN GPIO_Pin_11 |

| #define | MIOS32_SPI0_RCLK2_AF { } |

| #define | MIOS32_SPI0_SCLK_PORT GPIOA |

| #define | MIOS32_SPI0_SCLK_PIN GPIO_Pin_5 |

| #define | MIOS32_SPI0_SCLK_AF { GPIO_PinAFConfig(GPIOA, GPIO_PinSource5, GPIO_AF_SPI1); } |

| #define | MIOS32_SPI0_MISO_PORT GPIOA |

| #define | MIOS32_SPI0_MISO_PIN GPIO_Pin_6 |

| #define | MIOS32_SPI0_MISO_AF { GPIO_PinAFConfig(GPIOA, GPIO_PinSource6, GPIO_AF_SPI1); } |

| #define | MIOS32_SPI0_MOSI_PORT GPIOA |

| #define | MIOS32_SPI0_MOSI_PIN GPIO_Pin_7 |

| #define | MIOS32_SPI0_MOSI_AF { GPIO_PinAFConfig(GPIOA, GPIO_PinSource7, GPIO_AF_SPI1); } |

| #define | MIOS32_SPI1_PTR SPI2 |

| #define | MIOS32_SPI1_DMA_RX_PTR DMA1_Stream3 |

| #define | MIOS32_SPI1_DMA_RX_CHN DMA_Channel_0 |

| #define | MIOS32_SPI1_DMA_RX_IRQ_FLAGS (DMA_FLAG_TCIF3 | DMA_FLAG_TEIF3 | DMA_FLAG_HTIF3 | DMA_FLAG_FEIF3) |

| #define | MIOS32_SPI1_DMA_TX_PTR DMA1_Stream4 |

| #define | MIOS32_SPI1_DMA_TX_CHN DMA_Channel_0 |

| #define | MIOS32_SPI1_DMA_TX_IRQ_FLAGS (DMA_FLAG_TCIF4 | DMA_FLAG_TEIF4 | DMA_FLAG_HTIF4 | DMA_FLAG_FEIF4) |

| #define | MIOS32_SPI1_DMA_IRQ_CHANNEL DMA1_Stream3_IRQn |

| #define | MIOS32_SPI1_DMA_IRQHANDLER_FUNC void DMA1_Stream3_IRQHandler(void) |

| #define | MIOS32_SPI1_RCLK1_PORT GPIOB |

| #define | MIOS32_SPI1_RCLK1_PIN GPIO_Pin_12 |

| #define | MIOS32_SPI1_RCLK1_AF { GPIO_PinAFConfig(GPIOB, GPIO_PinSource12, GPIO_AF_SPI2); } |

| #define | MIOS32_SPI1_RCLK2_PORT GPIOD |

| #define | MIOS32_SPI1_RCLK2_PIN GPIO_Pin_10 |

| #define | MIOS32_SPI1_RCLK2_AF { } |

| #define | MIOS32_SPI1_SCLK_PORT GPIOB |

| #define | MIOS32_SPI1_SCLK_PIN GPIO_Pin_13 |

| #define | MIOS32_SPI1_SCLK_AF { GPIO_PinAFConfig(GPIOB, GPIO_PinSource13, GPIO_AF_SPI2); } |

| #define | MIOS32_SPI1_MISO_PORT GPIOB |

| #define | MIOS32_SPI1_MISO_PIN GPIO_Pin_14 |

| #define | MIOS32_SPI1_MISO_AF { GPIO_PinAFConfig(GPIOB, GPIO_PinSource14, GPIO_AF_SPI2); } |

| #define | MIOS32_SPI1_MOSI_PORT GPIOB |

| #define | MIOS32_SPI1_MOSI_PIN GPIO_Pin_15 |

| #define | MIOS32_SPI1_MOSI_AF { GPIO_PinAFConfig(GPIOB, GPIO_PinSource15, GPIO_AF_SPI2); } |

| #define | MIOS32_SPI2_PTR SPI3 |

| #define | MIOS32_SPI2_DMA_RX_PTR DMA1_Stream2 |

| #define | MIOS32_SPI2_DMA_RX_CHN DMA_Channel_0 |

| #define | MIOS32_SPI2_DMA_RX_IRQ_FLAGS (DMA_FLAG_TCIF2 | DMA_FLAG_TEIF2 | DMA_FLAG_HTIF2 | DMA_FLAG_FEIF2) |

| #define | MIOS32_SPI2_DMA_TX_PTR DMA1_Stream5 |

| #define | MIOS32_SPI2_DMA_TX_CHN DMA_Channel_0 |

| #define | MIOS32_SPI2_DMA_TX_IRQ_FLAGS (DMA_FLAG_TCIF5 | DMA_FLAG_TEIF5 | DMA_FLAG_HTIF5 | DMA_FLAG_FEIF5) |

| #define | MIOS32_SPI2_DMA_IRQ_CHANNEL DMA1_Stream2_IRQn |

| #define | MIOS32_SPI2_DMA_IRQHANDLER_FUNC void DMA1_Stream2_IRQHandler(void) |

| #define | MIOS32_SPI2_RCLK1_PORT GPIOA |

| #define | MIOS32_SPI2_RCLK1_PIN GPIO_Pin_15 |

| #define | MIOS32_SPI2_RCLK1_AF { GPIO_PinAFConfig(GPIOA, GPIO_PinSource15, GPIO_AF_SPI3); } |

| #define | MIOS32_SPI2_RCLK2_PORT GPIOB |

| #define | MIOS32_SPI2_RCLK2_PIN GPIO_Pin_8 |

| #define | MIOS32_SPI2_RCLK2_AF { } |

| #define | MIOS32_SPI2_SCLK_PORT GPIOB |

| #define | MIOS32_SPI2_SCLK_PIN GPIO_Pin_3 |

| #define | MIOS32_SPI2_SCLK_AF { GPIO_PinAFConfig(GPIOB, GPIO_PinSource3, GPIO_AF_SPI3); } |

| #define | MIOS32_SPI2_MISO_PORT GPIOB |

| #define | MIOS32_SPI2_MISO_PIN GPIO_Pin_4 |

| #define | MIOS32_SPI2_MISO_AF { GPIO_PinAFConfig(GPIOB, GPIO_PinSource4, GPIO_AF_SPI3); } |

| #define | MIOS32_SPI2_MOSI_PORT GPIOB |

| #define | MIOS32_SPI2_MOSI_PIN GPIO_Pin_5 |

| #define | MIOS32_SPI2_MOSI_AF { GPIO_PinAFConfig(GPIOB, GPIO_PinSource5, GPIO_AF_SPI3); } |

| #define | CCR_ENABLE ((uint32_t)0x00000001) |

Functions | |

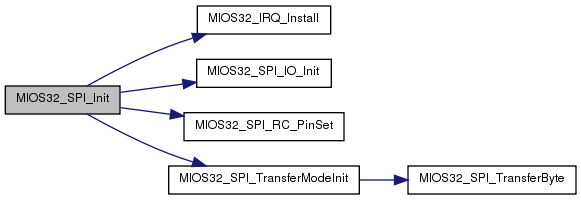

| s32 | MIOS32_SPI_Init (u32 mode) |

| s32 | MIOS32_SPI_IO_Init (u8 spi, mios32_spi_pin_driver_t spi_pin_driver) |

| s32 | MIOS32_SPI_TransferModeInit (u8 spi, mios32_spi_mode_t spi_mode, mios32_spi_prescaler_t spi_prescaler) |

| s32 | MIOS32_SPI_RC_PinSet (u8 spi, u8 rc_pin, u8 pin_value) |

| s32 | MIOS32_SPI_TransferByte (u8 spi, u8 b) |

| s32 | MIOS32_SPI_TransferBlock (u8 spi, u8 *send_buffer, u8 *receive_buffer, u16 len, void *callback) |

Detailed Description

Hardware Abstraction Layer for SPI ports of LPC17xx

Three ports are provided at J16 (SPI0), J8/9 (SPI1) and J19 (SPI2) of the MBHP_CORE_LTC17 module..

All SPI ports provide two RCLK (alias Chip Select) lines.

J16 is normaly connected to a SD Card

J8/9 is normaly connected to the SRIO chain to scan DIN/DOUT modules.

J19 doesn't support DMA transfers, so that MIOS32_SPI_TransferBlock() will consume CPU time (but the callback handling does work).

If SPI low-level functions should be used to access other peripherals, please ensure that the appr. MIOS32_* drivers are disabled (e.g. add 'define MIOS32_DONT_USE_SDCARD' and 'define MIOS32_DONT_USE_ENC28J60' to your mios_config.h file)

Note that additional chip select lines can be easily added by using the remaining free GPIOs of the core module. Shared SPI ports should be arbitrated with (FreeRTOS based) Mutexes to avoid collisions!

Hardware Abstraction Layer for SPI ports of STM32

Three ports are provided at J16 (SPI0), J8/9 (SPI1) and J19 (SPI2) of the MBHP_CORE_STM32 module..

J16 provides two RCLK (alias Chip Select) lines, and is normaly connected to a SD Card or/and an Ethernet Interface like ENC28J60.

J8/9 only supports a single RCLK line, and is normaly connected to the SRIO chain to scan DIN/DOUT modules.

J19 provides two RCLK (alias Chip Select) lines.

It's a software emulated SPI, therefore the selected spi_prescaler has no effect! Bytes are transfered so fast as possible. The usage of MIOS32_SPI_PIN_DRIVER_STRONG is strongly recommented ;)

DMA transfers are not supported by the emulation, so that MIOS32_SPI_TransferBlock() will consume CPU time (but the callback handling does work).

If SPI low-level functions should be used to access other peripherals, please ensure that the appr. MIOS32_* drivers are disabled (e.g. add 'define MIOS32_DONT_USE_SDCARD' and 'define MIOS32_DONT_USE_ENC28J60' to your mios_config.h file)

Note that additional chip select lines can be easily added by using the remaining free GPIOs of the core module. Shared SPI ports should be arbitrated with (FreeRTOS based) Mutexes to avoid collisions!

Hardware Abstraction Layer for SPI ports of STM32F4

Three ports are provided at J16 (SPI0), J8/9 (SPI1) and J19 (SPI2) of the MBHP_CORE_STM32F4 module..

J16 provides SPI + two RCLK (alias Chip Select) lines at 3V, and is normaly connected to a SD Card or/and an Ethernet Interface like ENC28J60.

J8/9 provides SPI + two RCLK lines at 5V. It is normally connected to the SRIO chain to scan DIN/DOUT modules.

J19 provides SPI + two RCLK lines at 5V. It's some kind of general purpose SPI, and used to communicate with various MBHP modules, such as MBHP_AOUT* and MBHP_AINSER*

If SPI low-level functions should be used to access other peripherals, please ensure that the appr. MIOS32_* drivers are disabled (e.g. add 'define MIOS32_DONT_USE_SDCARD' and 'define MIOS32_DONT_USE_ENC28J60' to your mios_config.h file)

Note that additional chip select lines can be easily added by using the remaining free GPIOs of the core module. Shared SPI ports should be arbitrated with (FreeRTOS based) Mutexes to avoid collisions!

Define Documentation

| #define CCR_ENABLE ((uint32_t)0x00000001) |

| #define CCR_ENABLE ((uint32_t)0x00000001) |

| #define MIOS32_SPI0_DMA_IRQ_CHANNEL DMA2_Stream2_IRQn |

| #define MIOS32_SPI0_DMA_IRQ_CHANNEL DMA1_Channel2_IRQn |

| #define MIOS32_SPI0_DMA_IRQHANDLER_FUNC void DMA2_Stream2_IRQHandler(void) |

| #define MIOS32_SPI0_DMA_IRQHANDLER_FUNC void DMA1_Channel2_IRQHandler(void) |

| #define MIOS32_SPI0_DMA_IRQHANDLER_FUNC void DMAChannel2_IRQHandler(void) |

| #define MIOS32_SPI0_DMA_RX_CHN DMA_Channel_3 |

| #define MIOS32_SPI0_DMA_RX_CHN 1 |

| #define MIOS32_SPI0_DMA_RX_IRQ_FLAGS (DMA_FLAG_TCIF2 | DMA_FLAG_TEIF2 | DMA_FLAG_HTIF2 | DMA_FLAG_FEIF2) |

| #define MIOS32_SPI0_DMA_RX_IRQ_FLAGS (DMA1_FLAG_TC2 | DMA1_FLAG_TE2 | DMA1_FLAG_HT2 | DMA1_FLAG_GL2) |

| #define MIOS32_SPI0_DMA_RX_PTR DMA2_Stream2 |

| #define MIOS32_SPI0_DMA_RX_PTR DMA1_Channel2 |

| #define MIOS32_SPI0_DMA_RX_REQ 1 |

| #define MIOS32_SPI0_DMA_TX_CHN DMA_Channel_3 |

| #define MIOS32_SPI0_DMA_TX_CHN 0 |

| #define MIOS32_SPI0_DMA_TX_IRQ_FLAGS (DMA_FLAG_TCIF3 | DMA_FLAG_TEIF3 | DMA_FLAG_HTIF3 | DMA_FLAG_FEIF3) |

| #define MIOS32_SPI0_DMA_TX_PTR DMA2_Stream3 |

| #define MIOS32_SPI0_DMA_TX_PTR DMA1_Channel3 |

| #define MIOS32_SPI0_DMA_TX_REQ 0 |

| #define MIOS32_SPI0_IN_INIT |

{ MIOS32_SYS_LPC_PINMODE(1, 24, 2); \

MIOS32_SYS_LPC_PINMODE(1, 23, 0); \

MIOS32_SYS_LPC_PINMODE(1, 22, 2); \

MIOS32_SYS_LPC_PINMODE(1, 21, 2); \

MIOS32_SYS_LPC_PINMODE(1, 20, 2); }

| #define MIOS32_SPI0_MISO_AF { GPIO_PinAFConfig(GPIOA, GPIO_PinSource6, GPIO_AF_SPI1); } |

| #define MIOS32_SPI0_MISO_INIT { MIOS32_SYS_LPC_PINSEL(1, 23, 3); } |

| #define MIOS32_SPI0_MISO_PIN GPIO_Pin_6 |

| #define MIOS32_SPI0_MISO_PIN GPIO_Pin_6 |

| #define MIOS32_SPI0_MISO_PORT GPIOA |

| #define MIOS32_SPI0_MISO_PORT GPIOA |

| #define MIOS32_SPI0_MOSI_AF { GPIO_PinAFConfig(GPIOA, GPIO_PinSource7, GPIO_AF_SPI1); } |

| #define MIOS32_SPI0_MOSI_INIT { MIOS32_SYS_LPC_PINSEL(1, 24, 3); } |

| #define MIOS32_SPI0_MOSI_PIN GPIO_Pin_7 |

| #define MIOS32_SPI0_MOSI_PIN GPIO_Pin_7 |

| #define MIOS32_SPI0_MOSI_PORT GPIOA |

| #define MIOS32_SPI0_MOSI_PORT GPIOA |

| #define MIOS32_SPI0_OD_INIT { LPC_PINCON->PINMODE_OD1 |= ((1 << 24) | (1 << 23) | (1 << 22) | (1 << 21) | (1 << 20)); } |

| #define MIOS32_SPI0_PP_INIT { LPC_PINCON->PINMODE_OD1 &= ~((1 << 24) | (1 << 23) | (1 << 22) | (1 << 21) | (1 << 20)); } |

| #define MIOS32_SPI0_PTR SPI1 |

| #define MIOS32_SPI0_PTR SPI1 |

| #define MIOS32_SPI0_PTR LPC_SSP0 |

| #define MIOS32_SPI0_RCLK1_AF { } |

| #define MIOS32_SPI0_RCLK1_INIT { MIOS32_SYS_LPC_PINSEL(1, 21, 0); MIOS32_SYS_LPC_PINDIR(1, 21, 1); } |

| #define MIOS32_SPI0_RCLK1_PIN GPIO_Pin_2 |

| #define MIOS32_SPI0_RCLK1_PIN GPIO_Pin_4 |

| #define MIOS32_SPI0_RCLK1_PORT GPIOB |

| #define MIOS32_SPI0_RCLK1_PORT GPIOA |

| #define MIOS32_SPI0_RCLK1_SET | ( | v | ) | { MIOS32_SYS_LPC_PINSET(1, 21, v); } |

| #define MIOS32_SPI0_RCLK2_AF { } |

| #define MIOS32_SPI0_RCLK2_INIT { MIOS32_SYS_LPC_PINSEL(1, 22, 0); MIOS32_SYS_LPC_PINDIR(1, 22, 1); } |

| #define MIOS32_SPI0_RCLK2_PIN GPIO_Pin_11 |

| #define MIOS32_SPI0_RCLK2_PIN GPIO_Pin_15 |

| #define MIOS32_SPI0_RCLK2_PORT GPIOD |

| #define MIOS32_SPI0_RCLK2_PORT GPIOC |

| #define MIOS32_SPI0_RCLK2_SET | ( | v | ) | { MIOS32_SYS_LPC_PINSET(1, 22, v); } |

| #define MIOS32_SPI0_SCLK_AF { GPIO_PinAFConfig(GPIOA, GPIO_PinSource5, GPIO_AF_SPI1); } |

| #define MIOS32_SPI0_SCLK_INIT { MIOS32_SYS_LPC_PINSEL(1, 20, 3); } |

| #define MIOS32_SPI0_SCLK_PIN GPIO_Pin_5 |

| #define MIOS32_SPI0_SCLK_PIN GPIO_Pin_5 |

| #define MIOS32_SPI0_SCLK_PORT GPIOA |

| #define MIOS32_SPI0_SCLK_PORT GPIOA |

| #define MIOS32_SPI1_DMA_IRQ_CHANNEL DMA1_Stream3_IRQn |

| #define MIOS32_SPI1_DMA_IRQ_CHANNEL DMA1_Channel4_IRQn |

| #define MIOS32_SPI1_DMA_IRQHANDLER_FUNC void DMA1_Stream3_IRQHandler(void) |

| #define MIOS32_SPI1_DMA_IRQHANDLER_FUNC void DMA1_Channel4_IRQHandler(void) |

| #define MIOS32_SPI1_DMA_IRQHANDLER_FUNC void DMAChannel4_IRQHandler(void) |

| #define MIOS32_SPI1_DMA_RX_CHN DMA_Channel_0 |

| #define MIOS32_SPI1_DMA_RX_CHN 3 |

| #define MIOS32_SPI1_DMA_RX_IRQ_FLAGS (DMA_FLAG_TCIF3 | DMA_FLAG_TEIF3 | DMA_FLAG_HTIF3 | DMA_FLAG_FEIF3) |

| #define MIOS32_SPI1_DMA_RX_IRQ_FLAGS (DMA1_FLAG_TC4 | DMA1_FLAG_TE4 | DMA1_FLAG_HT4 | DMA1_FLAG_GL4) |

| #define MIOS32_SPI1_DMA_RX_PTR DMA1_Stream3 |

| #define MIOS32_SPI1_DMA_RX_PTR DMA1_Channel4 |

| #define MIOS32_SPI1_DMA_RX_REQ 3 |

| #define MIOS32_SPI1_DMA_TX_CHN DMA_Channel_0 |

| #define MIOS32_SPI1_DMA_TX_CHN 2 |

| #define MIOS32_SPI1_DMA_TX_IRQ_FLAGS (DMA_FLAG_TCIF4 | DMA_FLAG_TEIF4 | DMA_FLAG_HTIF4 | DMA_FLAG_FEIF4) |

| #define MIOS32_SPI1_DMA_TX_PTR DMA1_Stream4 |

| #define MIOS32_SPI1_DMA_TX_PTR DMA1_Channel5 |

| #define MIOS32_SPI1_DMA_TX_REQ 2 |

| #define MIOS32_SPI1_IN_INIT |

{ MIOS32_SYS_LPC_PINMODE(0, 9, 2); \

MIOS32_SYS_LPC_PINMODE(0, 8, 0); \

MIOS32_SYS_LPC_PINMODE(0, 7, 2); \

MIOS32_SYS_LPC_PINMODE(0, 6, 2); \

MIOS32_SYS_LPC_PINMODE(3, 26, 2); }

| #define MIOS32_SPI1_MISO_AF { GPIO_PinAFConfig(GPIOB, GPIO_PinSource14, GPIO_AF_SPI2); } |

| #define MIOS32_SPI1_MISO_INIT { MIOS32_SYS_LPC_PINSEL(0, 8, 2); } |

| #define MIOS32_SPI1_MISO_PIN GPIO_Pin_14 |

| #define MIOS32_SPI1_MISO_PIN GPIO_Pin_14 |

| #define MIOS32_SPI1_MISO_PORT GPIOB |

| #define MIOS32_SPI1_MISO_PORT GPIOB |

| #define MIOS32_SPI1_MOSI_AF { GPIO_PinAFConfig(GPIOB, GPIO_PinSource15, GPIO_AF_SPI2); } |

| #define MIOS32_SPI1_MOSI_INIT { MIOS32_SYS_LPC_PINSEL(0, 9, 2); } |

| #define MIOS32_SPI1_MOSI_PIN GPIO_Pin_15 |

| #define MIOS32_SPI1_MOSI_PIN GPIO_Pin_15 |

| #define MIOS32_SPI1_MOSI_PORT GPIOB |

| #define MIOS32_SPI1_MOSI_PORT GPIOB |

| #define MIOS32_SPI1_OD_INIT { LPC_PINCON->PINMODE_OD0 |= ((1 << 9) | (1 << 8) | (1 << 7) | (1 << 6)); LPC_PINCON->PINMODE_OD3 |= ((1 << 26)); } |

| #define MIOS32_SPI1_PP_INIT { LPC_PINCON->PINMODE_OD0 &= ~((1 << 9) | (1 << 8) | (1 << 7) | (1 << 6)); LPC_PINCON->PINMODE_OD3 &= ~((1 << 26)); } |

| #define MIOS32_SPI1_PTR SPI2 |

| #define MIOS32_SPI1_PTR SPI2 |

| #define MIOS32_SPI1_PTR LPC_SSP1 |

| #define MIOS32_SPI1_RCLK1_AF { GPIO_PinAFConfig(GPIOB, GPIO_PinSource12, GPIO_AF_SPI2); } |

| #define MIOS32_SPI1_RCLK1_INIT { MIOS32_SYS_LPC_PINSEL(0, 6, 0); MIOS32_SYS_LPC_PINDIR(0, 6, 1); } |

| #define MIOS32_SPI1_RCLK1_PIN GPIO_Pin_12 |

| #define MIOS32_SPI1_RCLK1_PIN GPIO_Pin_12 |

| #define MIOS32_SPI1_RCLK1_PORT GPIOB |

| #define MIOS32_SPI1_RCLK1_PORT GPIOB |

| #define MIOS32_SPI1_RCLK1_SET | ( | v | ) | { MIOS32_SYS_LPC_PINSET(0, 6, v); } |

| #define MIOS32_SPI1_RCLK2_AF { } |

| #define MIOS32_SPI1_RCLK2_INIT { MIOS32_SYS_LPC_PINSEL(3, 26, 0); MIOS32_SYS_LPC_PINDIR(3, 26, 1); } |

| #define MIOS32_SPI1_RCLK2_PIN GPIO_Pin_10 |

| #define MIOS32_SPI1_RCLK2_PORT GPIOD |

| #define MIOS32_SPI1_RCLK2_SET | ( | v | ) | { MIOS32_SYS_LPC_PINSET(3, 26, v); } |

| #define MIOS32_SPI1_SCLK_AF { GPIO_PinAFConfig(GPIOB, GPIO_PinSource13, GPIO_AF_SPI2); } |

| #define MIOS32_SPI1_SCLK_INIT { MIOS32_SYS_LPC_PINSEL(0, 7, 2); } |

| #define MIOS32_SPI1_SCLK_PIN GPIO_Pin_13 |

| #define MIOS32_SPI1_SCLK_PIN GPIO_Pin_13 |

| #define MIOS32_SPI1_SCLK_PORT GPIOB |

| #define MIOS32_SPI1_SCLK_PORT GPIOB |

| #define MIOS32_SPI2_DMA_IRQ_CHANNEL DMA1_Stream2_IRQn |

| #define MIOS32_SPI2_DMA_IRQ_CHANNEL NULL |

| #define MIOS32_SPI2_DMA_IRQHANDLER_FUNC void DMA1_Stream2_IRQHandler(void) |

| #define MIOS32_SPI2_DMA_IRQHANDLER_FUNC NULL |

| #define MIOS32_SPI2_DMA_IRQHANDLER_FUNC NULL |

| #define MIOS32_SPI2_DMA_RX_CHN DMA_Channel_0 |

| #define MIOS32_SPI2_DMA_RX_IRQ_FLAGS (DMA_FLAG_TCIF2 | DMA_FLAG_TEIF2 | DMA_FLAG_HTIF2 | DMA_FLAG_FEIF2) |

| #define MIOS32_SPI2_DMA_RX_IRQ_FLAGS 0 |

| #define MIOS32_SPI2_DMA_RX_PTR DMA1_Stream2 |

| #define MIOS32_SPI2_DMA_RX_PTR NULL |

| #define MIOS32_SPI2_DMA_TX_CHN DMA_Channel_0 |

| #define MIOS32_SPI2_DMA_TX_IRQ_FLAGS (DMA_FLAG_TCIF5 | DMA_FLAG_TEIF5 | DMA_FLAG_HTIF5 | DMA_FLAG_FEIF5) |

| #define MIOS32_SPI2_DMA_TX_PTR DMA1_Stream5 |

| #define MIOS32_SPI2_DMA_TX_PTR NULL |

| #define MIOS32_SPI2_GET_MISO ( MIOS32_SPI2_MISO_PORT->IDR & MIOS32_SPI2_MISO_PIN ) |

| #define MIOS32_SPI2_IN_INIT |

{ MIOS32_SYS_LPC_PINMODE(0, 21, 2); \

MIOS32_SYS_LPC_PINMODE(0, 18, 2); \

MIOS32_SYS_LPC_PINMODE(0, 17, 0); \

MIOS32_SYS_LPC_PINMODE(0, 16, 2); \

MIOS32_SYS_LPC_PINMODE(0, 15, 2); }

| #define MIOS32_SPI2_MISO_AF { GPIO_PinAFConfig(GPIOB, GPIO_PinSource4, GPIO_AF_SPI3); } |

| #define MIOS32_SPI2_MISO_INIT { MIOS32_SYS_LPC_PINSEL(0, 17, 3); } |

| #define MIOS32_SPI2_MISO_PIN GPIO_Pin_4 |

| #define MIOS32_SPI2_MISO_PIN GPIO_Pin_7 |

| #define MIOS32_SPI2_MISO_PORT GPIOB |

| #define MIOS32_SPI2_MISO_PORT GPIOB |

| #define MIOS32_SPI2_MOSI_AF { GPIO_PinAFConfig(GPIOB, GPIO_PinSource5, GPIO_AF_SPI3); } |

| #define MIOS32_SPI2_MOSI_INIT { MIOS32_SYS_LPC_PINSEL(0, 18, 3); } |

| #define MIOS32_SPI2_MOSI_PIN GPIO_Pin_5 |

| #define MIOS32_SPI2_MOSI_PIN GPIO_Pin_5 |

| #define MIOS32_SPI2_MOSI_PORT GPIOB |

| #define MIOS32_SPI2_MOSI_PORT GPIOB |

| #define MIOS32_SPI2_OD_INIT { LPC_PINCON->PINMODE_OD0 |= ((1 << 21) | (1 << 18) | (1 << 17) | (1 << 16) | (1 << 15)); } |

| #define MIOS32_SPI2_PP_INIT { LPC_PINCON->PINMODE_OD0 &= ~((1 << 21) | (1 << 18) | (1 << 17) | (1 << 16) | (1 << 15)); } |

| #define MIOS32_SPI2_PTR SPI3 |

| #define MIOS32_SPI2_PTR NULL |

| #define MIOS32_SPI2_PTR LPC_SPI |

| #define MIOS32_SPI2_RCLK1_AF { GPIO_PinAFConfig(GPIOA, GPIO_PinSource15, GPIO_AF_SPI3); } |

| #define MIOS32_SPI2_RCLK1_INIT { MIOS32_SYS_LPC_PINSEL(0, 16, 0); MIOS32_SYS_LPC_PINDIR(0, 16, 1); } |

| #define MIOS32_SPI2_RCLK1_PIN GPIO_Pin_15 |

| #define MIOS32_SPI2_RCLK1_PIN GPIO_Pin_13 |

| #define MIOS32_SPI2_RCLK1_PORT GPIOA |

| #define MIOS32_SPI2_RCLK1_PORT GPIOC |

| #define MIOS32_SPI2_RCLK1_SET | ( | v | ) | { MIOS32_SYS_LPC_PINSET(0, 16, v); } |

| #define MIOS32_SPI2_RCLK2_AF { } |

| #define MIOS32_SPI2_RCLK2_INIT { MIOS32_SYS_LPC_PINSEL(0, 21, 0); MIOS32_SYS_LPC_PINDIR(0, 21, 1); } |

| #define MIOS32_SPI2_RCLK2_PIN GPIO_Pin_8 |

| #define MIOS32_SPI2_RCLK2_PIN GPIO_Pin_14 |

| #define MIOS32_SPI2_RCLK2_PORT GPIOB |

| #define MIOS32_SPI2_RCLK2_PORT GPIOC |

| #define MIOS32_SPI2_RCLK2_SET | ( | v | ) | { MIOS32_SYS_LPC_PINSET(0, 21, v); } |

| #define MIOS32_SPI2_SCLK_AF { GPIO_PinAFConfig(GPIOB, GPIO_PinSource3, GPIO_AF_SPI3); } |

| #define MIOS32_SPI2_SCLK_INIT { MIOS32_SYS_LPC_PINSEL(0, 15, 3); } |

| #define MIOS32_SPI2_SCLK_PIN GPIO_Pin_3 |

| #define MIOS32_SPI2_SCLK_PIN GPIO_Pin_6 |

| #define MIOS32_SPI2_SCLK_PORT GPIOB |

| #define MIOS32_SPI2_SCLK_PORT GPIOB |

| #define MIOS32_SPI2_SET_MOSI | ( | b | ) | { MIOS32_SPI2_MOSI_PORT->BSRR = (b) ? MIOS32_SPI2_MOSI_PIN : (MIOS32_SPI2_MOSI_PIN << 16); } |

| #define MIOS32_SPI2_SET_SCLK_0 { MIOS32_SPI2_SCLK_PORT->BRR = MIOS32_SPI2_SCLK_PIN; } |

| #define MIOS32_SPI2_SET_SCLK_1 { MIOS32_SPI2_SCLK_PORT->BSRR = MIOS32_SPI2_SCLK_PIN; } |

Function Documentation

Initializes SPI pins

- Parameters:

-

[in] mode currently only mode 0 supported

- Returns:

- < 0 if initialisation failed

| s32 MIOS32_SPI_IO_Init | ( | u8 | spi, | |

| mios32_spi_pin_driver_t | spi_pin_driver | |||

| ) |

(Re-)initializes SPI IO Pins By default, all output pins are configured with weak open drain drivers for 2 MHz

- Parameters:

-

[in] spi SPI number (0, 1 or 2) [in] spi_pin_driver configures the driver strength: - MIOS32_SPI_PIN_DRIVER_STRONG: configures outputs for up to 50 MHz

-

MIOS32_SPI_PIN_DRIVER_STRONG_OD: configures outputs as open drain for up to 50 MHz (allows voltage shifting via pull-resistors)

Note: LPC17xx doesn't support Open Drain Mode for SCK and MOSI pin! - MIOS32_SPI_PIN_DRIVER_WEAK: configures outputs for up to 2 MHz (better EMC)

-

MIOS32_SPI_PIN_DRIVER_WEAK_OD: configures outputs as open drain for up to 2 MHz (allows voltage shifting via pull-resistors)

Note: LPC17xx doesn't support Open Drain Mode for SCK and MOSI pin!

- Returns:

- 0 if no error

- -1 if disabled SPI port selected

- -2 if unsupported SPI port selected

- -3 if unsupported pin driver mode

(Re-)initializes SPI IO Pins By default, all output pins are configured with weak open drain drivers for 2 MHz

- Parameters:

-

[in] spi SPI number (0, 1 or 2) [in] spi_pin_driver configures the driver strength: - MIOS32_SPI_PIN_DRIVER_STRONG: configures outputs for up to 50 MHz

- MIOS32_SPI_PIN_DRIVER_STRONG_OD: configures outputs as open drain for up to 50 MHz (allows voltage shifting via pull-resistors)

- MIOS32_SPI_PIN_DRIVER_WEAK: configures outputs for up to 2 MHz (better EMC)

- MIOS32_SPI_PIN_DRIVER_WEAK_OD: configures outputs as open drain for up to 2 MHz (allows voltage shifting via pull-resistors)

- Returns:

- 0 if no error

- -1 if disabled SPI port selected

- -2 if unsupported SPI port selected

- -3 if unsupported pin driver mode

Controls the RC (Register Clock alias Chip Select) pin of a SPI port

- Parameters:

-

[in] spi SPI number (0, 1 or 2) [in] rc_pin RCLK pin (0 or 1 for RCLK1 or RCLK2) [in] pin_value 0 or 1

- Returns:

- 0 if no error

- -1 if disabled SPI port selected

- -2 if unsupported SPI port selected

- -3 if unsupported RCx pin selected

| s32 MIOS32_SPI_TransferBlock | ( | u8 | spi, | |

| u8 * | send_buffer, | |||

| u8 * | receive_buffer, | |||

| u16 | len, | |||

| void * | callback | |||

| ) |

Transfers a block of bytes via DMA.

- Parameters:

-

[in] spi SPI number (0, 1 or 2) [in] send_buffer pointer to buffer which should be sent.

If NULL, 0xff (all-one) will be sent.[in] receive_buffer pointer to buffer which should get the received values.

If NULL, received bytes will be discarded.[in] len number of bytes which should be transfered [in] callback pointer to callback function which will be executed from DMA channel interrupt once the transfer is finished. If NULL, no callback function will be used, and MIOS32_SPI_TransferBlock() will block until the transfer is finished.

- Returns:

- >= 0 if no error during transfer

- -1 if disabled SPI port selected

- -2 if unsupported SPI port selected

- -3 if function has been called during an ongoing DMA transfer

- -4 too many bytes (len too long)

- -5 no bytes (len is 0)

Transfers a block of bytes via DMA.

- Parameters:

-

[in] spi SPI number (0, 1 or 2) [in] send_buffer pointer to buffer which should be sent.

If NULL, 0xff (all-one) will be sent.[in] receive_buffer pointer to buffer which should get the received values.

If NULL, received bytes will be discarded.[in] len number of bytes which should be transfered [in] callback pointer to callback function which will be executed from DMA channel interrupt once the transfer is finished. If NULL, no callback function will be used, and MIOS32_SPI_TransferBlock() will block until the transfer is finished.

- Returns:

- >= 0 if no error during transfer

- -1 if disabled SPI port selected

- -2 if unsupported SPI port selected

- -3 if function has been called during an ongoing DMA transfer

Transfers a byte to SPI output and reads back the return value from SPI input

- Parameters:

-

[in] spi SPI number (0, 1 or 2) [in] b the byte which should be transfered

- Returns:

- >= 0: the read byte

- -1 if disabled SPI port selected

- -2 if unsupported SPI port selected

- -3 if unsupported SPI mode configured via MIOS32_SPI_TransferModeInit()

| s32 MIOS32_SPI_TransferModeInit | ( | u8 | spi, | |

| mios32_spi_mode_t | spi_mode, | |||

| mios32_spi_prescaler_t | spi_prescaler | |||

| ) |

(Re-)initializes SPI peripheral transfer mode By default, all SPI peripherals are configured with MIOS32_SPI_MODE_CLK1_PHASE1 and MIOS32_SPI_PRESCALER_128

- Parameters:

-

[in] spi SPI number (0, 1 or 2) [in] spi_mode configures clock and capture phase: - MIOS32_SPI_MODE_CLK0_PHASE0: Idle level of clock is 0, data captured at rising edge

- MIOS32_SPI_MODE_CLK0_PHASE1: Idle level of clock is 0, data captured at falling edge

- MIOS32_SPI_MODE_CLK1_PHASE0: Idle level of clock is 1, data captured at falling edge

- MIOS32_SPI_MODE_CLK1_PHASE1: Idle level of clock is 1, data captured at rising edge

[in] spi_prescaler configures the SPI speed: - MIOS32_SPI_PRESCALER_2: sets clock rate 0.02 uS @ 100 MHz (50 MBit/s) (only supported for spi==0 and spi==1, spi2 uses 8 instead)

- MIOS32_SPI_PRESCALER_4: sets clock rate 0.04 uS @ 100 MHz (25 MBit/s) (only supported for spi==0 and spi==1, spi2 uses 8 instead)

- MIOS32_SPI_PRESCALER_8: sets clock rate 0.08 uS @ 100 MHz (12.5 MBit/s)

- MIOS32_SPI_PRESCALER_16: sets clock rate 0.16 uS @ 100 MHz (6.25 MBit/s)

- MIOS32_SPI_PRESCALER_32: sets clock rate 0.32 uS @ 100 MHz (3.125 MBit/s)

- MIOS32_SPI_PRESCALER_64: sets clock rate 0.64 uS @ 100 MHz (1.563 MBit/s)

- MIOS32_SPI_PRESCALER_128: sets clock rate 1.28 uS @ 100 MHz (0.781 MBit/s)

- MIOS32_SPI_PRESCALER_256: sets clock rate 2.56 uS @ 100 MHz (0.391 MBit/s)

- Returns:

- 0 if no error

- -1 if disabled SPI port selected

- -2 if unsupported SPI port selected

- -3 if invalid spi_prescaler selected

- -4 if invalid spi_mode selected

(Re-)initializes SPI peripheral transfer mode By default, all SPI peripherals are configured with MIOS32_SPI_MODE_CLK1_PHASE1 and MIOS32_SPI_PRESCALER_128

- Parameters:

-

[in] spi SPI number (0, 1 or 2) [in] spi_mode configures clock and capture phase: - MIOS32_SPI_MODE_CLK0_PHASE0: Idle level of clock is 0, data captured at rising edge

- MIOS32_SPI_MODE_CLK0_PHASE1: Idle level of clock is 0, data captured at falling edge

- MIOS32_SPI_MODE_CLK1_PHASE0: Idle level of clock is 1, data captured at falling edge

- MIOS32_SPI_MODE_CLK1_PHASE1: Idle level of clock is 1, data captured at rising edge

[in] spi_prescaler configures the SPI speed: - MIOS32_SPI_PRESCALER_2: sets clock rate 27.7~ nS @ 72 MHz (36 MBit/s) (only supported for spi==0, spi1 uses 4 instead)

- MIOS32_SPI_PRESCALER_4: sets clock rate 55.5~ nS @ 72 MHz (18 MBit/s)

- MIOS32_SPI_PRESCALER_8: sets clock rate 111.1~ nS @ 72 MHz (9 MBit/s)

- MIOS32_SPI_PRESCALER_16: sets clock rate 222.2~ nS @ 72 MHz (4.5 MBit/s)

- MIOS32_SPI_PRESCALER_32: sets clock rate 444.4~ nS @ 72 MHz (2.25 MBit/s)

- MIOS32_SPI_PRESCALER_64: sets clock rate 888.8~ nS @ 72 MHz (1.125 MBit/s)

- MIOS32_SPI_PRESCALER_128: sets clock rate 1.7~ nS @ 72 MHz (0.562 MBit/s)

- MIOS32_SPI_PRESCALER_256: sets clock rate 3.5~ nS @ 72 MHz (0.281 MBit/s)

- Returns:

- 0 if no error

- -1 if disabled SPI port selected

- -2 if unsupported SPI port selected

- -3 if invalid spi_prescaler selected

- -4 if invalid spi_mode selected

(Re-)initializes SPI peripheral transfer mode By default, all SPI peripherals are configured with MIOS32_SPI_MODE_CLK1_PHASE1 and MIOS32_SPI_PRESCALER_128

- Parameters:

-

[in] spi SPI number (0, 1 or 2) [in] spi_mode configures clock and capture phase: - MIOS32_SPI_MODE_CLK0_PHASE0: Idle level of clock is 0, data captured at rising edge

- MIOS32_SPI_MODE_CLK0_PHASE1: Idle level of clock is 0, data captured at falling edge

- MIOS32_SPI_MODE_CLK1_PHASE0: Idle level of clock is 1, data captured at falling edge

- MIOS32_SPI_MODE_CLK1_PHASE1: Idle level of clock is 1, data captured at rising edge

[in] spi_prescaler configures the SPI speed: - MIOS32_SPI_PRESCALER_2: sets clock rate 27.7~ nS @ 72 MHz (36 MBit/s) (only supported for spi==0, spi1 uses 4 instead)

- MIOS32_SPI_PRESCALER_4: sets clock rate 55.5~ nS @ 72 MHz (18 MBit/s)

- MIOS32_SPI_PRESCALER_8: sets clock rate 111.1~ nS @ 72 MHz (9 MBit/s)

- MIOS32_SPI_PRESCALER_16: sets clock rate 222.2~ nS @ 72 MHz (4.5 MBit/s)

- MIOS32_SPI_PRESCALER_32: sets clock rate 444.4~ nS @ 72 MHz (2.25 MBit/s)

- MIOS32_SPI_PRESCALER_64: sets clock rate 888.8~ nS @ 72 MHz (1.125 MBit/s)

- MIOS32_SPI_PRESCALER_128: sets clock rate 1.7~ uS @ 72 MHz (0.562 MBit/s)

- MIOS32_SPI_PRESCALER_256: sets clock rate 3.5~ uS @ 72 MHz (0.281 MBit/s)

- Returns:

- 0 if no error

- -1 if disabled SPI port selected

- -2 if unsupported SPI port selected

- -3 if invalid spi_prescaler selected

- -4 if invalid spi_mode selected

(Re-)initializes SPI peripheral transfer mode By default, all SPI peripherals are configured with MIOS32_SPI_MODE_CLK1_PHASE1 and MIOS32_SPI_PRESCALER_128

- Parameters:

-

[in] spi SPI number (0, 1 or 2) [in] spi_mode configures clock and capture phase: - MIOS32_SPI_MODE_CLK0_PHASE0: Idle level of clock is 0, data captured at rising edge

- MIOS32_SPI_MODE_CLK0_PHASE1: Idle level of clock is 0, data captured at falling edge

- MIOS32_SPI_MODE_CLK1_PHASE0: Idle level of clock is 1, data captured at falling edge

- MIOS32_SPI_MODE_CLK1_PHASE1: Idle level of clock is 1, data captured at rising edge

[in] spi_prescaler configures the SPI speed: - MIOS32_SPI_PRESCALER_2: sets clock rate 23.4 nS @ 84 MHz (42.67 MBit/s)

- MIOS32_SPI_PRESCALER_4: sets clock rate 46,8 nS @ 84 MHz (21.33 MBit/s)

- MIOS32_SPI_PRESCALER_8: sets clock rate 93.8 nS @ 84 MHz (10.67 MBit/s)

- MIOS32_SPI_PRESCALER_16: sets clock rate 187 nS @ 84 MHz (5.333 MBit/s)

- MIOS32_SPI_PRESCALER_32: sets clock rate 375 nS @ 84 MHz (2.667 MBit/s)

- MIOS32_SPI_PRESCALER_64: sets clock rate 750 nS @ 84 MHz (1.333 MBit/s)

- MIOS32_SPI_PRESCALER_128: sets clock rate 1.5 uS @ 84 MHz (0.667 MBit/s)

- MIOS32_SPI_PRESCALER_256: sets clock rate 3 uS @ 84 MHz (0.333 MBit/s)

- Returns:

- 0 if no error

- -1 if disabled SPI port selected

- -2 if unsupported SPI port selected

- -3 if invalid spi_prescaler selected

- -4 if invalid spi_mode selected

1.6.1

1.6.1